## **Summary**

#### **Features**

- Connects one ABL series 16-channel SiPM base

- Connects one AB4 series 4-channel SiPM base through a cable adapter

- Wideband DC-coupled signal path

- Buffers 16 SiPM signals for an external ADC

- Sums 16 SiPM signals with gain & offset adjustment

- Internal constant-fraction discriminator

- SiPM array bias is provided by a precision variable HV power supply with over-current shutdown, voltage monitor, and current monitor

## **Standard accessories**

- 3 ft. 26-conductor micro-pitch cable assembly

- 1 ft. DB25F ribbon cable assembly

- 12V, 1A desktop power supply

#### **Local controls**

- SiPM bias voltage

- Analog sum gain & offset; DC or AC coupling

- Discriminator threshold

- HV power supply over-current fault reset

## Local output signals

- Bias voltage, bias current, SiPM temperature

- Analog sum / CFD zero-crossing / threshold

- TTL trigger input / output

### I/O Port signals for an external DAQ

- 16 buffered SiPM signals

- SiPM Base temperature

- Bias voltage control and HV status

- Trigger

## **SiPM Base signals**

- 16 SiPM signals

- SiPM bias voltage

- Amplifier power

- Base temperature

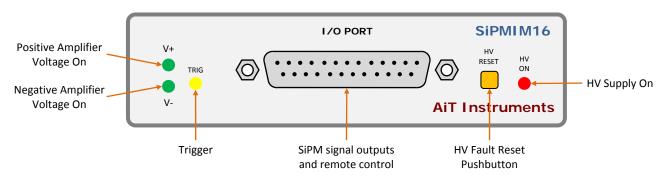

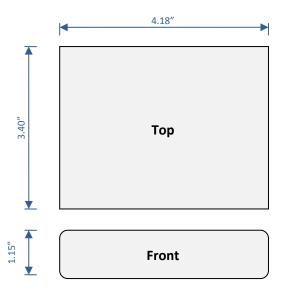

**Enclosure Front**

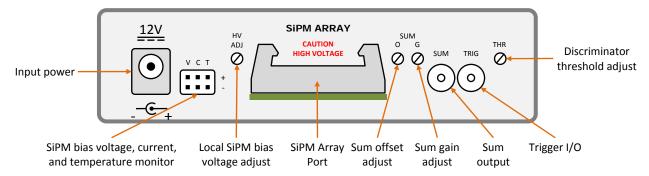

**Enclosure Back**

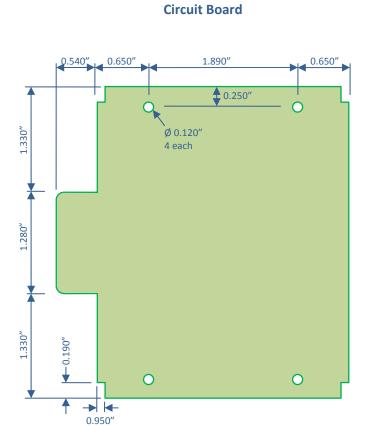

Circuit Board

# **ABL Series 16-Channel SiPM Readout System**

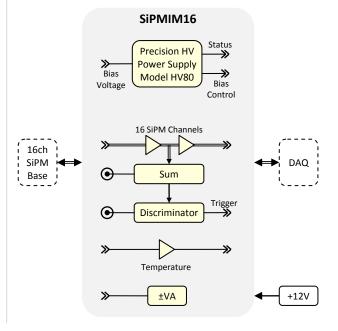

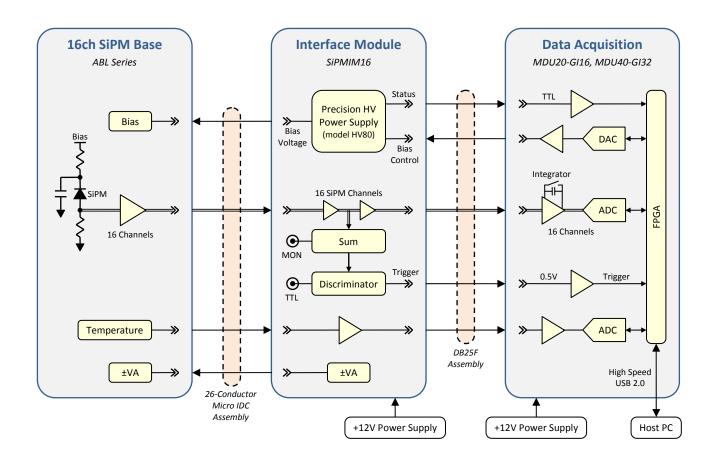

#### Summary

A 16-channel SiPM array readout system consists of an ABL series 16-channel SiPM Base, a SiPMIM16 ("IM16") Interface Module, and a 16/32-channel simultaneous sampling USB gated integrator model MDU20-GI16 or MDU40-GI32.

### **SiPM Base and Interface Module**

The ABL Base connects to the IM16 through a micro-pitch ribbon cable that permits versatile placement of the Base. The IM16 powers the Base, buffers SiPM signals, and forms a trigger from the discriminated analog sum of all SiPM signals.

#### MDU20-GI16 and MDU40-GI32

The MDU20-GI16 has 16 simultaneous gated integrators followed by 16 simultaneous sampling ADCs. Each integrator is preceded by a 100ns analog delay to compensate for trigger latency. A 16-bit DAC controls SiPM bias and a 16-bit ADC monitors SiPM temperature. The IM16 connects to the MDU20-GI16 through a DB25F cable assembly. The MDU40-GI32 is a dual version of the MDU20-GI16 capable of controlling two IM16s.

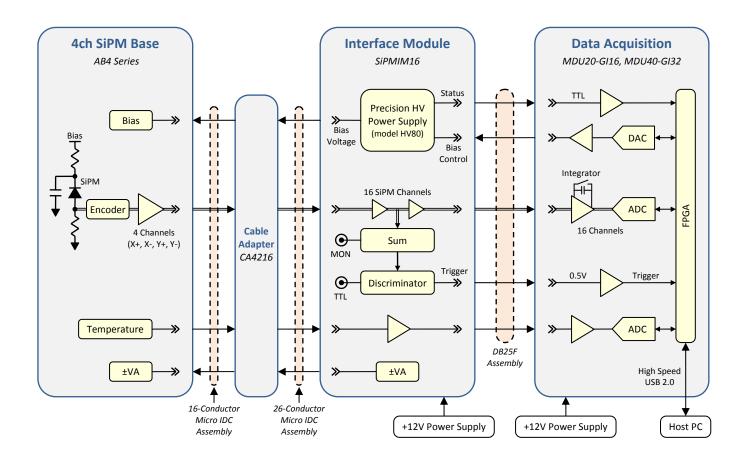

## **AB4 Series 4-Channel SiPM Readout System**

#### Summary

A 4-channel SiPM array readout system consists of an AB4 series 4-channel SiPM Base, a SiPMIM16 ("IM16") Interface Module, and a 16/32-channel simultaneous sampling USB gated integrator model MDU20-GI16 or MDU40-GI32. A cable adapter is required to connect the AB4 to the IM16.

### **SiPM Base and Interface Module**

The AB4 Base connects to the IM16 through a micro-pitch ribbon cable that permits versatile placement of the Base. The IM16 powers the Base, buffers SiPM signals, and forms a trigger from the discriminated analog sum of all SiPM signals.

#### MDU20-GI16 and MDU40-GI32

The MDU20-GI16 has 16 simultaneous gated integrators followed by 16 simultaneous sampling ADCs. Each integrator is preceded by a 100ns analog delay to compensate for trigger latency. A 16-bit DAC controls SiPM bias and a 16-bit ADC monitors SiPM temperature. The IM16 connects to the MDU20-GI16 through a DB25F cable assembly. The MDU40-GI32 is a dual version of the MDU20-GI16 capable of controlling two IM16s.

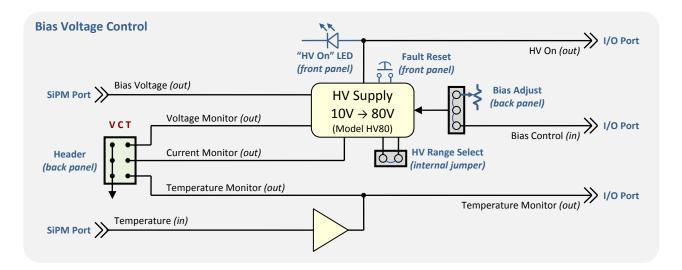

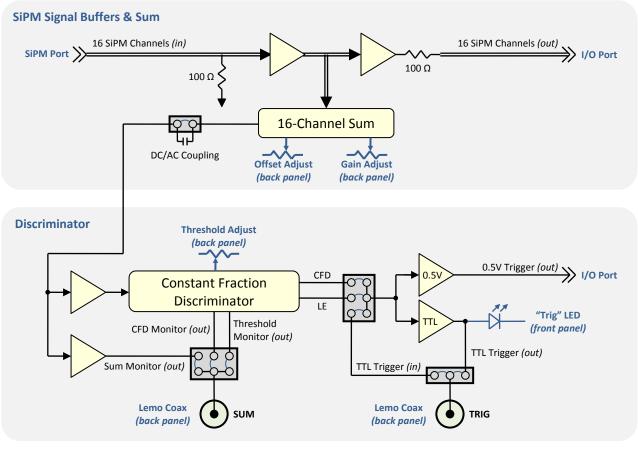

### **Architecture**

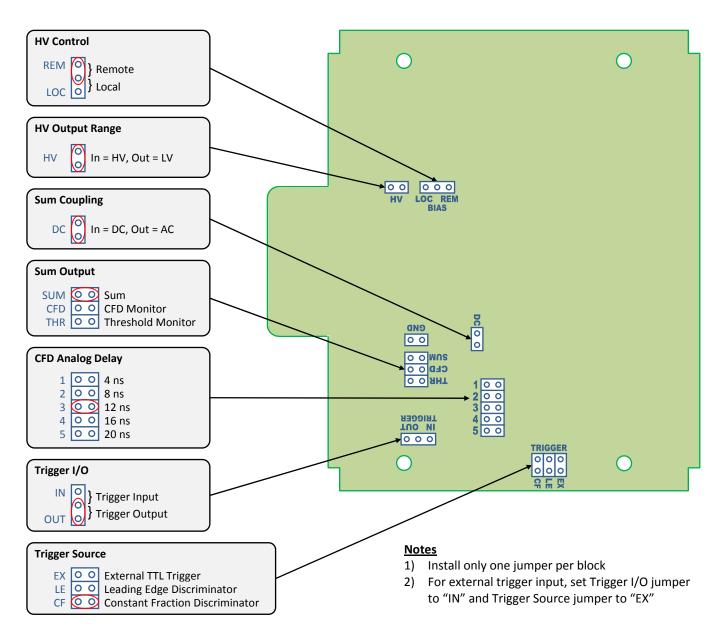

(out) = output from the IM16 (in) = input to the IM16 = Jumper (select only one position per block)

## 16-Channel Silicon Photomultiplier Interface Module

## **Specifications**

**SiPM Signal Buffers**

Rise time < 3 nsBandwidth (in  $\rightarrow$  out) 120 MHz

Gain (in  $\rightarrow$  out) 0.25 (100Ω source, 50Ω load) Input voltage  $\pm 3V$  max., 100Ω input impedance

Output voltage  $\pm 1V$  max.  $(100\Omega load)$ , 50mA max.,  $100\Omega$  output impedance

**SiPM Signal Sum**

Rise time < 4 ns

Bandwidth 80 MHz at min. gain, 50 MHz at max. gain Gain adjust  $0.25 \rightarrow 2.5$  (25-turn potentiometer)

Input offset adjust  $\pm 650$ mV, with in  $\rightarrow$  sum gain = 1 (25-turn potentiometer)

Coupling DC or AC; (jumper selectable)

AC-coupling time constant 10 μs

Output voltage  $\pm 1V$  max.  $(50\Omega load)$ , 50mA max.,  $50\Omega$  output impedance

Trigger

Options Constant fraction discriminator, leading-edge discriminator, external

5V TTL, none; (jumper selectable)

I/O Port trigger output level 0.5V

External trigger input level 5V TTL, 100Ω input impedance

External trigger output level 5V TTL, 24mA

**Constant Fraction Discriminator**

Timing resolution 100 ps min. Threshold  $0V \rightarrow -1V$  Fraction 40% Output pulse width 20 ns

Analog delay 5-tap, 4 ns per tap, 12 ns nominal; (jumper selectable)

Leading-edge discriminator Time-over-threshold output from CFD circuit; (jumper selectable)

Threshold & CFD monitors Shared with sum monitor; (jumper selectable)

Gain 1

Bandwidth 100 MHz

Output voltage  $\pm 1V$  max. (50 $\Omega$  load), 50mA max., 50 $\Omega$  output impedance

**Temperature Monitor**

Input voltage +3V max.,  $1 M\Omega$  input impedance

Output voltage +3V max., 20mA max., 50Ω output impedance

Gain 1

**Bias Power Supply**

Output voltage  $10V \rightarrow 80V$ , 2mA max.

Load regulation < 0.01% Setpoint linearity < 0.01%

Initial accuracy < 0.05%, trimmable

Local bias control (25-turn potentiometer, jumper selectable range)

High range  $64V \rightarrow 80V$ Low range  $25V \rightarrow 32V$

Datasheet

(Preliminary) Rev. 12/13

#### 16-Channel Silicon Photomultiplier Interface Module

Remote bias control  $0V \rightarrow 2.5V$  control =  $0V \rightarrow 80V$  bias

1 M $\Omega$  input impedance

Voltage monitor  $0V \rightarrow 2.5V$  output =  $0V \rightarrow 80V$  bias

20mA max.,  $50\Omega$  output impedance

Current monitor  $0V \rightarrow 2V$  output =  $0mA \rightarrow 2mA$  bias current, 10% min. accuracy

20mA max.,  $50\Omega$  output impedance

Output over-current fault

Fault reset

>2mA output current disables HV power supply until reset

Resets HV power supply fault latch and momentarily bypasses the

over-current fault circuit to enable the HV power supply

Fault bypass time 1 second typ.

Local reset Front-panel pushbutton

Remote reset Remote bias control transition from 0V to >0.5V

**WARNING** Repeating HV reset during a persistent fault condition may damage

system components. Identify and remove the cause of the fault, restart the HV power supply at a safe voltage, then slowly restore

normal bias voltage.

Base Amplifier Voltage ±2.8V, 200mA max.

Power Supply Requirements +12V DC, 170mA typ. (Iq, no signal, no load, HV on)

**LEDs**

V+ Green = Positive amplifier voltage on V- Green = Negative amplifier voltage on

TRIG Yellow = Trigger

HV ON Red = HV power supply enabled

**HV Reset Pushbutton** Resets a HV power supply fault

Mechanical

PCB overall dimensions 3.725" x 3.940"

PCB mounting holes, 4 each 0.12" diameter, accepts #4 hardware

Do not exceed 0.25" dia. mounting hardware

Enclosure dimensions 4.18" (W), 3.40"(L), 1.15"(H)

Enclosure material Aluminum

Connectors

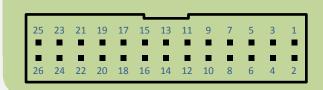

SiPM ARRAY 26 pin, 2 row latch-eject header, 0.050" pin pitch

Mating assembly = Samtec FFSD-13-D-XX.XX-01-N

(XX.XX = length in inches)

SUM, TRIG Lemo EP.00 coaxial receptacle VCT 6 pin 2-row header, 0.1" pitch

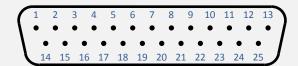

I/O PORT 25 pin male D-sub

12V Circular barrel power jack, 2.1mm ID, 5.5mm OD, center positive

### **Front Panel**

## **Back Panel**

## Mechanical

### **Enclosure**

# **4X4 SiPM Array Channel Map**

Top, facing array

| A1 | B1 | C1 | D1 |

|----|----|----|----|

| A2 | B2 | C2 | D2 |

| A3 | В3 | C3 | D3 |

| A4 | B4 | C4 | D4 |

Bottom (bond area)

## **Connectors**

## **SiPM Array Port**

26-pin 0.050" latch-eject header

**Enclosure Back Panel**

PCB Top View

| Pin | Function | Pin | Function |

|-----|----------|-----|----------|

| 1   | D4       | 2   | Temp     |

| 3   | D1       | 4   | GND      |

| 5   | D2       | 6   | D3       |

| 7   | C4       | 8   | GND      |

| 9   | C1       | 10  | C3       |

| 11  | C2       | 12  | -VA      |

| 13  | B4       | 14  | GND      |

| 15  | B1       | 16  | +VA      |

| 17  | B2       | 18  | В3       |

| 19  | A4       | 20  | GND      |

| 21  | A1       | 22  | A3       |

| 23  | A2       | 24  | GND      |

| 25  | +Bias    | 26  | GND      |

## I/O Port

25-pin male D-sub

| Pin | Function     | Pin | Function |

|-----|--------------|-----|----------|

| 1   | A1           | 14  | B1       |

| 2   | C1           | 15  | D1       |

| 3   | GND          | 16  | A2       |

| 4   | B2           | 17  | C2       |

| 5   | D2           | 18  | GND      |

| 6   | A3           | 19  | В3       |

| 7   | C3           | 20  | D3       |

| 8   | GND          | 21  | A4       |

| 9   | B4           | 22  | C4       |

| 10  | D4           | 23  | GND      |

| 11  | Bias Control | 24  | Temp     |

| 12  | HV Status    | 25  | Trigger  |

| 13  | GND          |     |          |

# **VCT Monitor**

6-pin header

| Pin | Function     | Pin | Function |

|-----|--------------|-----|----------|

| 1   | Temperature  | 2   | GND      |

| 3   | Bias Current | 4   | GND      |

| 5   | Bias Voltage | 6   | GND      |

## **Jumpers**

= Default jumper position

16-Channel Silicon Photomultiplier Interface Module

Datasheet (Preliminary) Rev. 12/13

## **Operation**

### **Summary**

Routine operating parameters can be adjusted through back-panel potentiometers. Occasional settings are configured by on-board jumpers, requiring enclosure disassembly. SiPM bias voltage control, HV status, SiPM temperature, and trigger are available on the I/O Port for remote operation.

When the IM16 is installed in a new application, a one-time manual setup is typically needed to adjust most IM16 settings. After the initial setup, normal operation may require few small adjustments.

#### Typical Setup for an Unadjusted IM16

- 1. Disconnect power

- 2. Set jumpers as follows

a. CFD Analog Delay = 12 ns

b. Sum Output = SUM

c. Trigger I/O = OUT

d. Trigger Source = CFD

e. Sum Coupling = DC (if AC coupling is used then sum offset calibration is not needed)

f. HV Control = set as appropriate g. HV Range = set as appropriate

- 3. Set potentiometers as follows

- a. HV ADJ = fully counterclockwise (lowest bias voltage)

- b. SUM Gain = 12.5 turns clockwise (medium gain)

c. THR = fully counterclockwise (lowest threshold)

Note: Do not adjust *Pulse Width* and *Current Limit* potentiometers

- 4. Connect cables

- a. Connect a Base using the micro IDC cable

- b. Connect *SUM* and *TRIG* outputs to two DC-coupled oscilloscope channels with 50  $\Omega$  input termination, and configure the oscilloscope to trigger on *TRIG*

- c. Connect a voltmeter to the Bias Voltage Monitor

- 5. Place the Base, with SiPM attached, in a low-light application capable of producing optical pulses

- 6. Begin operation

- a. Power the IM16

- b. Press HV RESET to enable the HV power supply if needed

- c. Allow the system to stabilize for at least 15 minutes

- d. TRIG may be noisy because of the low threshold

- 7. Set bias voltage

- a. Increase HV control voltage (turn HV ADJ clockwise if local) to the SiPM operating voltage

- b. If the bias voltage or optical signal level is too high then an over-current condition may disable the HV power supply. If this occurs then lower the bias voltage, press HV RESET, and slowly restore the normal bias voltage. Avoid restarting HV at high bias voltages.

- 8. Calibrate offset

(Preliminary) Rev. 12/13

16-Channel Silicon Photomultiplier Interface Module

- a. This adjustment is not necessary if the sum is AC coupled

- b. Adjust SUM Offset until the sum baseline is near zero (< 10 mV) as seen on the oscilloscope

- c. A valid trigger is not needed for this adjustment (use oscilloscope auto-trigger)

- 9. Set gain

- a. With SiPM signals present, adjust SUM Gain to the desired level

- b. A 50% full-scale gain setting, approx. 12.5/25 turns, is a typical starting reference

- c. For high gain, the sum offset may require re-adjustment

- 10. Set threshold

- a. With SiPM signals present, turn THR clockwise until the threshold is above the noise

## **Typical Setup for Normal Operation**

- 1. Connect the Base with the IM16 power off

- 2. Optionally connect an oscilloscope to SUM and TRIG

- 3. Power the IM16

- 4. Press HV RESET to clear a possible over-current fault resulting from power-up inrush current

- 5. With SiPM signals present, adjust HV ADJ, SUM Offset, and SUM Gain as needed

## **Remote Operation**

- 1. Set the LOC/REM BIAS jumper to REM

- 2. If the HV is off then cycle the remote bias control voltage to zero then above 0.5V to clear the fault

- 3. If the remote bias control voltage is greater than 0.5V then it will not be possible to reset the HV power supply using the HV RESET pushbutton. This condition is independent of the LOC/REM BIAS jumper.

#### **External Discriminator Operation**

- 1. Set the SUM Output jumper to SUM

- 2. Adjust SUM Offset and SUM Gain as needed

- 3. Connect the SUM output to an external discriminator

- 4. If the external discriminator will trigger an ADC connected to the I/O Port then the TRIG must be configured as a TTL trigger input:

- a. Set the TRIGGER I/O jumper to IN

- b. Set the TRIGGER Source jumper to EX

- c. Connect the external trigger TTL output to the TRIG connector

## **SiPM Bias Current Limit**

The HV power supply will automatically disable if the output current exceeds its current limit. The over-current circuit is designed to protect only the HV power supply from damaging load currents. It is not designed to protect other equipment or personnel.

Datasheet

(Preliminary) Rev. 12/13

16-Channel Silicon Photomultiplier Interface Module

An over-current fault may occur during normal operation due to high SiPM bias current, high load capacitance, or high optical signal levels. While the protection circuit may offer incidental protection to the SiPM in some cases, it is not designed to prevent damage to the SiPM.

A fault reset clears an over-current fault latch and momentarily bypasses the protection circuit. Repeating HV resets during a persistent fault condition may damage system components. Identify and remove the cause of the fault, restart the HV power supply at a safe voltage, then slowly restore normal bias voltage.

### **CFD Analog Delay Selection**

The CFD circuit has a jumper selectable 5-tap analog delay line. The recommended delay for most applications is 12ns. A different analog delay can be selected by changing the position of CFD delay jumper to one of five taps. If the desired delay setting is unavailable then the socketed SIP delay line may be replaced with a different delay. Increasing the delay will increase trigger latency.

#### **Leading-Edge Discriminator**

The leading edge discriminator is part of the CFD circuit. It may be used as a trigger but its timing and noise performance may be inferior to the CFD. The discriminator output pulse is time-over-threshold with no pulse width control.

### **Sum DC/AC Coupling**

Installing the *Sum Coupling* jumper will select DC coupling of the sum signal. DC coupling requires adjusting the sum offset to zero for correct operation of the internal CFD. DC coupling is typically recommended for high pulse rate applications.

Removing the *Sum Coupling* jumper will select AC coupling of the sum signal. AC coupling does not require DC offset adjustment. The RC time constant will produce an offset shift during high-rate operation.

### **Sum Offset Sensitivity to SiPM Bias Voltage**

If the sum is DC coupled then changes in bias voltage may require offset adjustment to maintain the sum baseline near zero for proper discriminator operation. Small bias voltage changes typically do not require offset adjustment. Offset adjustment is not required if the sum is AC coupled.

16-Channel Silicon Photomultiplier Interface Module

Datasheet (Preliminary) Rev. 12/13

## **System Assembly Guidelines**

## **SiPM Cable Assembly**

The SiPM micro-pitch cable assembly must be inserted firmly into the latch/eject header until the latches lock around the connector. Correct orientation results in the cable exiting directly away from the Interface Module without interference, and the red index conductor is located on the right side of the connector, facing back of the unit.

#### **DB25F Cable Assembly**

A flat ribbon cable assembly is recommended. Use the shortest cable necessary.

## **High Voltage**

This device must be used only by personnel trained and qualified in safe handling, installation, and operation of high voltage equipment. The optional enclosure does not protect against high voltage exposure.

During operation, high voltage will normally be present in the following components:

- Interface Module circuit board

- SiPM Port signal connector pins

- Exposed base of the SiPM Port signal connector

- SiPM signal cable

- SiPM Base

## **Enclosure & PCB Mounting**

This device is intended to be incorporated into another system or product. The circuit board may be mounted using standard #4 hardware. Mounting hardware should not exceed 0.25" diameter contact area with the circuit board. Allow for adequate ventilation space around the circuit board.

The optional enclosure is provided to simplify bench testing and permits mounting into 19" rack panels. Unassembled enclosure components may have sharp edges. Observe appropriate handling precautions.

# **Safety Information**

# WARNING – High Voltage

- High voltage may be present during operation

- High voltage stored on capacitors may be present after power is removed

- Improper handling may result in personnel injury or equipment damage

This high-voltage device must be used only by personnel trained and qualified in safe handling, installation, and operation of high-voltage equipment.

# **CAUTION – Electrostatic Discharge (ESD) Sensitivity**

The circuit board can be damaged by electrostatic discharge. Observe precautions for handling electrostatic sensitive devices. Handle only at static-safe workstations.

## **High-Gain Photodetectors**

High-gain photodetectors such as silicon photomultipliers may conduct damaging currents if exposed to high optical signal levels while the bias voltage is applied, or if the bias voltage exceeds the recommended operating range. These devices must be operated only in low-light conditions, and only within the manufacturer's recommended bias voltage range.

## **Handling and Disassembly**

This product may be provided with or without a protective enclosure. Disassembled enclosure components and circuit boards may contain sharp edges. Take appropriate safety precautions while assembling or disassembling the enclosure and handling disassembled components.

## **Indoor Use Only**

Do not operate this product in a wet/damp environment. Do not operate in an explosive atmosphere.

Use of this product, and AiT Instruments' liability related to use of this product, is further governed by AiT Instruments' standard terms and conditions of sale, which were provided upon purchase of this product.